AI 浪潮席卷产业的当下,所有人的目光都聚焦在 CPU、GPU、存储器这些 " 台前主角 " 身上,却少有人留意,IP 行业正从一个稳定的 " 慢赛道 " 一跃成为整个半导体生态中最炙手可热的板块。

如果说芯片设计公司是 AI 时代的 " 淘金者 ",那么半导体 IP 厂商就是那个 " 卖铲人 " ——在每一颗 AI 芯片的背后,都离不开 IP 厂商提供的处理器内核、高速接口和各类功能模块。而当淘金热愈演愈烈时,最先赚得盆满钵满的往往是那些出售工具和补给的人。

AI 淘金热里,IP 才是隐形赢家

半导体 IP 市场的热度,首先体现在持续创新高的市场规模上。鉴于 2025 年全球 IP 市场规模的官方数据尚未披露,本部分分析将优先采用 2024 年的统计数据。

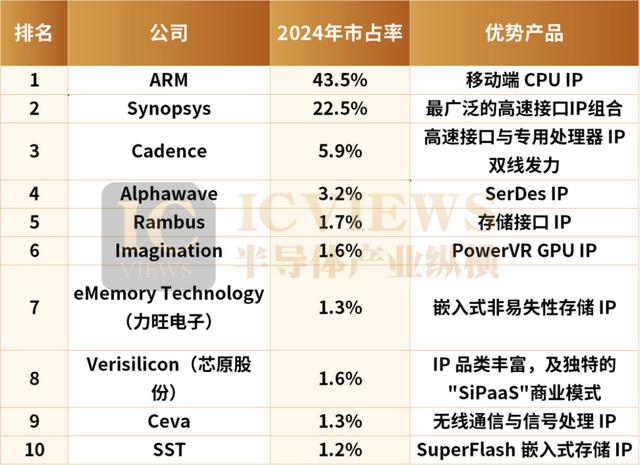

据行业机构 IPnest 发布数据显示,2024 年全球半导体设计 IP(知识产权)市场规模达到 84.916 亿美元(折合约 85 亿美元),较 2023 年的 70.625 亿美元增长 20.2%,创下历史新高。其中全球设计 IP 市场 TOP10 厂商营收合计 70.89 亿美元,同比增长 22.8%,市场份额从 2023 年的 81.7% 提升至 83.7%。其中,ARM、Synopsys 两家企业合计占据 66% 的市场份额。

据行业机构 IPnest 发布数据显示,2024 年全球半导体设计 IP(知识产权)市场规模达到 84.916 亿美元(折合约 85 亿美元),较 2023 年的 70.625 亿美元增长 20.2%,创下历史新高。其中全球设计 IP 市场 TOP10 厂商营收合计 70.89 亿美元,同比增长 22.8%,市场份额从 2023 年的 81.7% 提升至 83.7%。其中,ARM、Synopsys 两家企业合计占据 66% 的市场份额。

从 2016 年至 2024 年,全球 IP 市场增长了 145%,其中,Synopsys 和 Cadence 的增长率分别达到 326% 和 321%,而 ARM 的增长率为 124%。

IP 十强,优势解析

在移动端 CPU IP 领域,ARM 是当之无愧的龙头,是智能手机、AIoT、汽车电子等领域大都选择该架构。ARM 的全栈化 IP 矩阵覆盖从低功耗 Cortex-M 系列(MCU)、高性能 Cortex-A 系列(手机 / 服务器),到 AI 专用 Neoverse 系列(数据中心 / AI 芯片),以及 Mali GPU、Ethos NPU 等完整 IP 组合,满足从边缘到云端的全场景需求。

在生态壁垒方面,目前全球有超千家芯片设计公司基于 ARM 架构开发产品,形成 "ARM 架构→芯片→软件生态→终端用户 " 的完整闭环,也是 RISC-V 架构最大的竞争对手。

Synopsys 和Cadence均为 EDA 龙头,其 IP 业务是其整体战略的关键一环,旨在与自家的 EDA 工具形成合力,特别是在数字后端、定制设计和系统级验证等领域提供强大的 IP 支持。

其中 Synopsys 提供行业最广泛的基础 IP 组合,同时拥有业界最广泛的高速接口 IP 组合,涵盖 PCIe、CXL、以太网、HBM、Chiplet 互连(UCIe)等所有关键协议。

Cadence 侧重高速接口与专用处理器 IP 双线发力,高速 SerDes、HBM 接口性能顶尖,旗下 Tensilica DSP/AI 处理器 IP 具有独特优势,与模拟 / 混合信号 EDA 工具链融合更紧密。

Alphawave专注于 112G/224G 等超高速 SerDes IP,技术性能对标 Synopsys/Cadence,在数据中心、AI 芯片、Chiplet 领域快速崛起。并且在 UCIe、CXL 等 Chiplet 互联标准上深度布局,为 AI 加速器、HPC 芯片提供高速 Die-to-Die 互联 IP,是 Chiplet 架构普及的核心受益者。

Rambus专注于 DDR、LPDDR、HBM 等高速存储器接口 IP,是 AI 加速器、数据中心、智能手机内存互联的核心供应商,尤其在 HBM3/HBM4 等高端存储接口领域技术壁垒极高。LPDDR5T/5x 等低功耗存储器控制器 IP,专为移动设备、AIoT 设计,在功耗控制上业界领先。

Imagination的 PowerVR GPU IP 以低功耗、高能效比著称,在图形渲染、AI 推理融合方面优势显著,支持多精度计算,适配智能手机、汽车电子等严苛功耗场景。

eMemory Technology(力旺电子)是全球最大的嵌入式非易失性存储 IP 供应商,提供 OTP、MTP、Flash、ReRAM 等全品类 NVM IP,广泛应用于 MCU、IoT、汽车电子、AIoT 等领域。

Verisilicon(芯原股份)技术优势是 IP 品类丰富,其独特的 "SiPaaS" 商业模式将半导体 IP 授权与一站式芯片定制服务有机结合,形成了完整的产业生态闭环。 通过平台化的服务模式,芯原能够为客户大幅缩短芯片开发周期,降低研发成本,提高产品竞争力。

Ceva的无线通信 IP 全球领先,可提供蓝牙、Wi-Fi、5G、UWB 等无线通信 IP,是 IoT、智能手机、汽车电子等领域无线互联的核心供应商,尤其在低功耗蓝牙 IP 领域市占率极高。

SST(冠捷半导体)的技术优势是 SuperFlash 嵌入式存储 IP。其专注于嵌入式闪存技术,提供高可靠性、低功耗的 Flash IP,广泛应用于消费电子、工业、汽车等领域,是 MCU、IoT 芯片的核心存储 IP 供应商。

然而,比整体增长更值得关注的,是市场内部正在发生的结构性变化。

接口 IP,增速迅猛

半导体 IP 主要分为处理器类(CPU/GPU/NPU)、接口类(PCIe/CXL/DDR)、车规级、互联类(Chiplet 相关)等。过去,处理器 IP(如 CPU、GPU 内核)是市场的绝对主角。但随着生成式 AI 的崛起,系统性能的瓶颈不再仅仅取决于单一计算核心的强弱,而是由 " 计算能力、内存带宽、互连带宽、系统延迟 " 中最慢的一环决定。算力正在从 " 决定性优势 " 走向 " 基础设施化 ",而决定数据能否高效流动的 " 连接 " 能力,则成为了新的权力中心。

这一转变直接反映在 IP 市场的品类消长上:

在过去很长一段时间里,处理器 IP 都是半导体 IP 市场的核心,占据绝对主导地位。但 2024 年有线接口 IP 的增长率达到 23.5%,高于处理器类 IP 增速,成为 IP 市场增长的主要驱动力。这一领域的增长,主要得益于 PCIe、DDR、以太网和 D2D 等协议的广泛应用。具体来看:

AI 算力瓶颈倒逼,高端接口成为 " 刚需 "

当大模型迈入千亿、万亿参数时代,AI 芯片、HPC 芯片对数据传输带宽的渴求呈指数级飙升,PCIe 6.0/7.0、CXL 3.0、HBM4、224G/400G SerDes 这些高速接口,早已不是简单的辅助模块,而是制约算力释放的 " 命门 "。更关键的是,高端接口的设计门槛堪称业内 " 硬骨头 ",涉及高频信号完整性、低功耗控制等多重技术难题,企业自研不仅要投入上亿元研发成本,更要面对流片失败的巨大风险,而 Synopsys、Cadence、Alphawave 等厂商的成熟商用接口 IP,自然成为芯片厂商的最优解。

Chiplet 架构普及,拉动接口 IP 用量激增

Chiplet 芯粒架构的普及,彻底颠覆了传统芯片设计逻辑,多芯粒异构集成模式下,不同功能芯粒的协同工作,完全依赖 UCIe、SerDes 等 Die-to-Die 接口 IP,每颗 Chiplet 需搭载多组接口实现高速互通,既拉动接口 IP 用量几乎翻倍,也推动其技术规格持续迭代。

先进制程演进,接口 IP 愈发不可替代

3nm、2nm 先进制程的演进,进一步放大了接口 IP 的不可替代性:制程节点提升带来的线宽缩小、信号干扰加剧,让接口设计难度呈几何级数攀升,自研周期拉长、成本翻倍,商用 IP 的性价比与安全性优势愈发凸显;再叠加 PCIe、CXL 等接口协议每 2-3 年一次的快速迭代,以及 SoC 芯片集成度提升带来的 IP 复用刚需,接口 IP 的增长动能被彻底激活。

接口 IP 的爆发式增长,不仅重构了半导体 IP 市场的品类权重,更让 "IP 话语权 " 成为产业竞争的核心战场,那些手握核心 IP 的企业,既能凭借技术壁垒占据产业链高地,也能通过生态绑定抢占市场份额。正是在这样的产业逻辑下,一场围绕 IP 的布局战悄然打响,巨头们纷纷通过收购、自研等方式,加速构建属于自己的 IP 护城河。

巨头抢滩,争夺 IP 话语权

格芯,相继完成两笔收购

去年 7 月至今年 1 月,格芯完成了两笔关于 IP 的收购,分别是收购的 EDA+IP 龙头企业 Synopsys 的 ARC 处理器 IP 解决方案业务、AI 和处理器 IP 领先供应商 MIPS。

其中 MIPS 拥有 40 余年处理器 IP 研发经验,核心产品包括基于 RISC-V 架构的 Atlas 系列 CPU IP、高性能实时处理器 IP,主打中高端边缘计算场景;Synopsys 的 ARC 处理器 IP 业务覆盖ARC-V(RISC-V)和 ARC CPU IP、DSP IP、神经网络处理单元(NPU)IP,以及相关软件开发工具,主打低功耗、低成本、高可配置性。

两者整合后,格芯可以提供超低功耗 IoT 处理器到高性能边缘 AI 处理器、从 CPU/DSP 到 NPU 的全栈式计算 IP 解决方案。值得注意的是,这两笔收购还有另一个核心价值,即让格芯成为 RISC-V 生态核心玩家。RISC-V 作为开源指令集架构,凭借开放、灵活、低成本、自主可控的优势,正在边缘计算、物联网、汽车电子等领域抢占 ARM 的市场份额。

晶圆代工厂向客户提供的 IP 多为接口类的基础模块,而 Arm 等公司会针对部分制程节点定制其处理器核心。但通过此次收购,格芯将成为首家基于开源 RISC-V 指令集架构、面向计算应用场景提供处理器 IP 的代工厂商。

在晶圆代工领域,台积电凭借先进制程(3nm/2nm)、极致良率、完善生态,占据晶圆代工市场约七成的市场份额,尤其在高端 AI 芯片、手机 SoC 领域几乎垄断。而格芯早在 2018 年就已决定放弃先进制程研发,聚焦 14/12nm 及以上特色工艺。因此,选择错位竞争、聚焦差异化,或许会是格芯的成功路径之一。

高通收购 Alphawave

Alphawave Semi 最初叫 Alphawave IP。正如其名,它是一家纯粹的 IP 供应商,正如上文所言,其核心拳头产品是 SerDes(解复用器),覆盖 PCIe、CXL、UCIe 等协议。这是一种让数据在芯片内外进行超高速传输的关键技术。去年 6 月,美国芯片巨头高通宣布以约 24 亿美元现金收购 Alphawave。据悉,Alphawave 的客户包括亚马逊 AWS 等头部企业。

此次收购被视为高通 " 重返数据中心 " 的关键一步。2017 年,高通曾推出 ARM 架构服务器芯片 Centriq 2400,但因 Arm 生态薄弱及市场竞争压力退出。2021 年,高通以 14 亿美元收购高性能 Arm 服务器芯片设计公司 Nuvia,重新积蓄技术能量。

此次收购 Alphawave,高通旨在 AI 数据中心和高性能计算的网络传输技术方面的短板。通过整合 Alphawave 的高速互联 IP,高通可优化芯片间数据传输效率,降低 AI 算力部署成本,尤其在 UCIe 小芯片互联领域抢占先机。

此外,IP 大厂也在通过收购、技术研发等路线,增强自身实力。2025 年 4 月 17 日,Cadence 宣布,已与 Arm 达成最终协议,收购 Arm 的 Artisan 基础 IP 业务。该业务涵盖标准单元库、内存编译器以及针对领先代工厂先进工艺节点优化的通用 I/O(GPIO)。此次交易将增强 Cadence 不断扩展的设计 IP 产品线,其核心产品包括领先的协议和接口 IP、内存接口 IP、适用于最先进节点的 SerDes IP,以及即将收购的 Secure-IC 公司提供的嵌入式安全 IP。Cadence 硅片解决方案事业部高级副总裁兼总经理 Boyd Phelps 表示:随着 Arm 的 Artisan IP 的加入,Cadence 将进入基础 IP 市场,并支持设计服务和小芯片产品的新增长。

AI 算力时代的到来,彻底重塑了半导体产业的价值逻辑,半导体 IP 从 " 产业配角 " 跃升为 " 核心中枢 ",成为决定芯片性能、研发效率与产业话语权的关键变量。未来,随着 AI 算力需求的持续提升、Chiplet 架构的普及与 RISC-V 的崛起,半导体 IP 市场将迎来更激烈的竞争与更深刻的变革。

来源:半导体产业纵横